## Università degli Studi di Milano - Corso Architettura degli elaboratori I

Prof. Borghese – Appello 20.02.2024

Cognome e nome dello studente:

*Matricola:*

Numero pagine:

- 2. [3] Disegnare il diagramma di flusso di un algoritmo della moltiplicazione binaria intera firmware a 4 bit, e implementarlo in un circuito <u>contenente tre registri</u>: 1 registro moltiplicando a 8 bit, 1 registro moltiplicatore a 4 bit e 1 registro risultato a 8 bit. Evidenziare tutti i cammini relativi al data path, dimensionarli e definire la loro funzione.

- 3. [4] Descrivere come si possa modificare il datapath del circuito disegnato per l'esercizio 2, mantenendo i 3 registri specificati, per eseguire anche l'operazione di divisione intera di numeri su 4 bit. Quali segnali di controllo occorre aggiungere? Motivare le modifiche e definire chiaramente la loro funzione. Mostrare come varia il contenuto di tutti e 3 i registri durante i primi 2 passi di esecuzione della divisione 7 : 2.

- 4. [5] Costruire il circuito (FSM) che implementa l'unità di controllo del circuito costruito al punto 2. Calcolare complessità e cammino critico. In quanti cicli di clock viene ultimata una moltiplicazione? Semplificare per via analitica le funzioni di stato prossimo.

- 5. [2] Scrivere una funzione logica a piacere, di 3 variabili in ingresso e 2 in uscita, il cui circuito associato abbia cammino critico pari a 2 e complessità pari a 5 [2].

- 6. [2] Scrivere la funzione logica ottenuta per l'esercizio 5, nella prima e nella seconda forma canonica.

- 7. [2] Mediante manipolazione algebrica, trasformare la prima forma canonica nella seconda o viceversa.

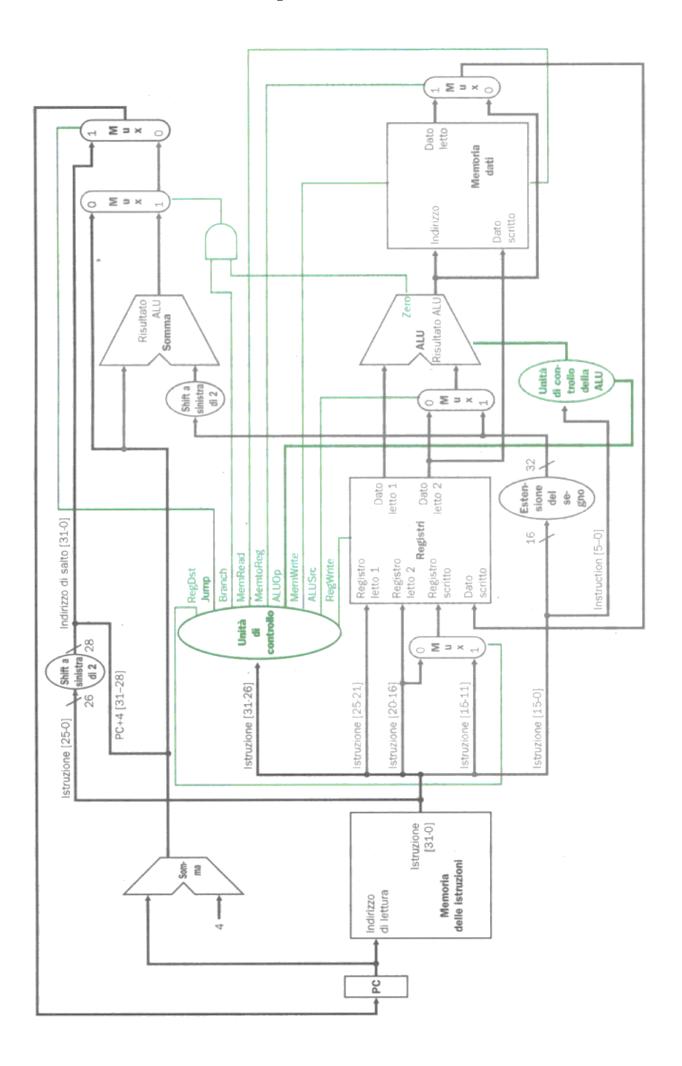

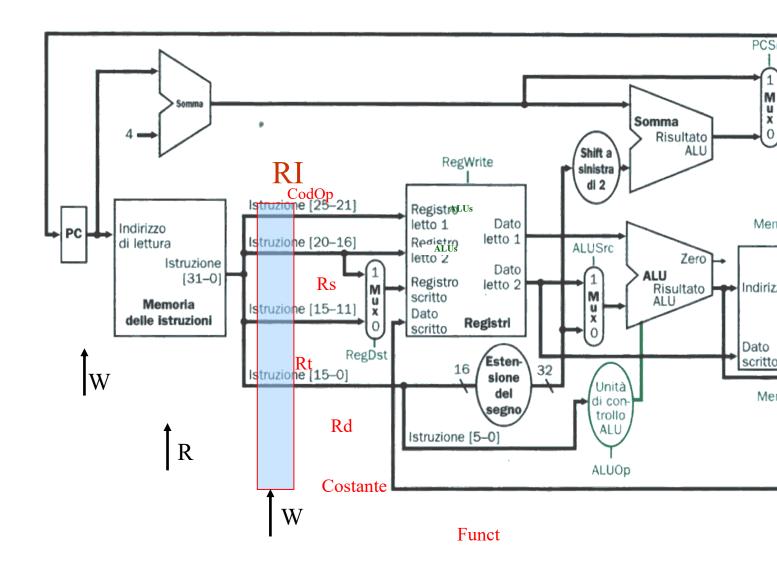

- 9. [4] Specificare il contenuto di <u>tutti i bus</u> della CPU riportata in Figura 1 quando è in esecuzione l'istruzione di beq \$1, \$2, ind\_salto, sapendo che il codice operativo dell'istruzione beq è 4. Si supponga inoltre che l'indirizzo della beq sia 0x4000 0000 e che l'indirizzo di salto sia 0x4000 0040. Evidenziare i bus che trasportano dati utili per l'esecuzione dell'istruzione. Tradurre l'istruzione assembler di beq in linguaggio macchina e rappresentarla in notazione esadecimale. Scrivere in linguaggio macchina l'istruzione di salto incondizionato che consente di saltare allo stesso indirizzo di salto. Il codice operativo dell'istruzione di jump è 2.

- 10. [2] Disegnare il ciclo di esecuzione di un'istruzione su un'architettura MIPS a singolo ciclo. Quante fasi si distinguono? Quando l'architettura capisce di che istruzione si tratta? I componenti appartenenti a quali fasi vengono configurati dall'unità di controllo? Perché? Cos'è un'ISA? Possono due CPU avere la stessa ISA? Due CPU diverse devono avere una ISA necessariamente diversa? Perché?

- 11. [2] Definire i diversi formati delle istruzioni MIPS e specificare la funzione dei diversi campi. Descrivere come viene suddivisa in modo logico per convenzione una memoria principale dai processori MIPS e quali sono le ragioni per la scelta dei confini dei diversi segmenti.

- 12. [2] Definire chiaramente cosa si intende per sommatore ad anticipazione di riporto, e quale sia il razionale per la sua implementazione.

13. [3] Costruire il circuito hardware della moltiplicazione intera di numeri su 3 bit. Calcolare complessità e cammino critico.

Figura 1